Yesterday Intel detailed their first clean-slate CPU core micro-architecture since “Nehalem”, which is codenamed “Sunny Cove”. Over the past 10 years the 9 generations of Core processors have been basically refinements of “Nehalem”, even the most recent “Coffee Lake” parts. Intel is now planning a clean-slate core design, much like what AMD did with “Zen”. This will allow Intel to introduce significant IPC gains over the current generation. If you look at the past 3 generations of Intel micro-architectures the IPC growth curve has remained flat.

Keep in mind that “Sunny Cove” is the codename for the core design. Intel previously would use codenames which would include not only the cores, but also uncore and entire dies. It is up to Intel’s chip designers to design dies with these cores, which would also feature a future generation iGPU, and a next-generation uncore that integrates PCIe gen 4.0 and DDR5 memory. Intel has detailed “Sunny Cove” as far as IPC gains, a new ISA (new instruction sets and hardware capabilities, including AVX-512), and improved scalability (ability to increase core-counts without running into latency problems).

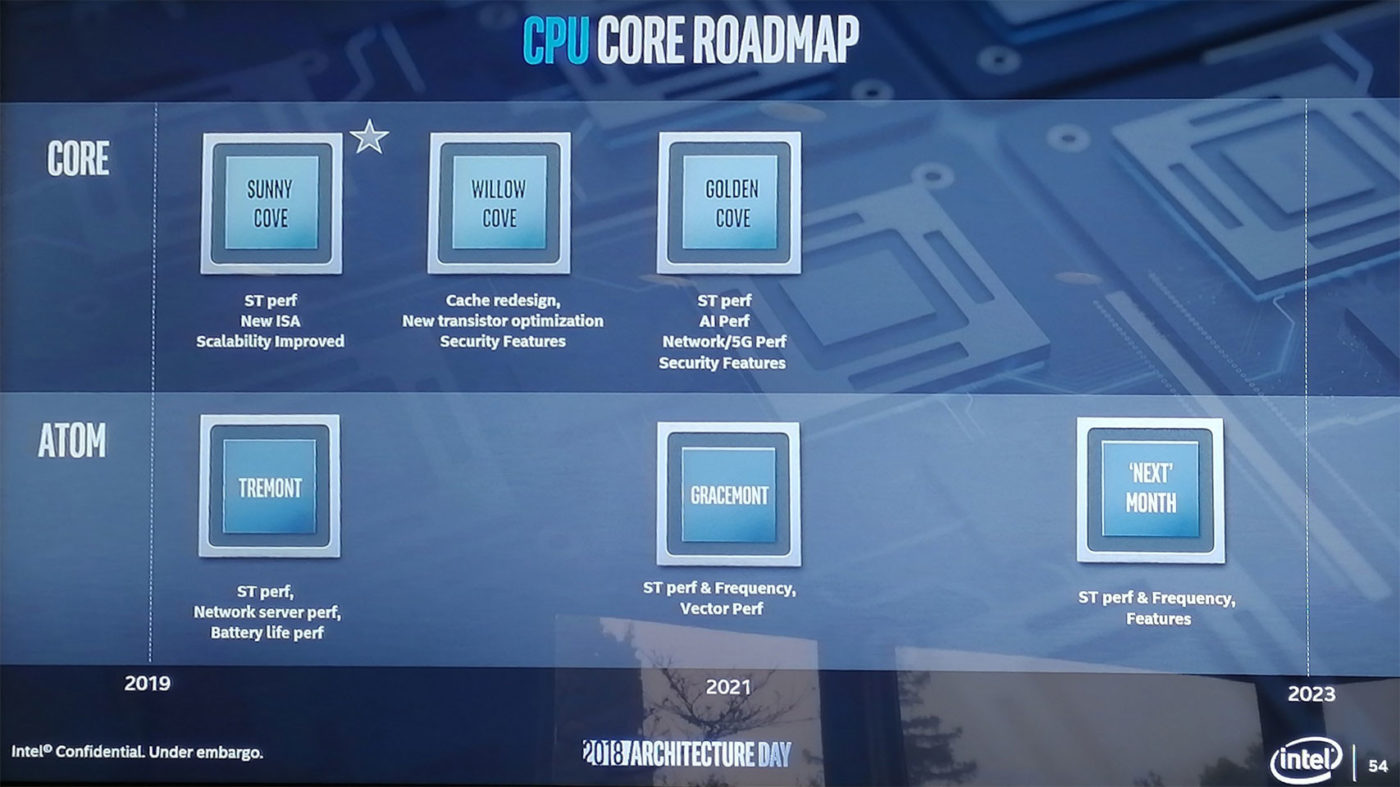

Intel expects the first products featuring “Sunny Cove” cores to be ready as early as 2019, and we will be built on Intel’s 10 nm DUV silicon fabrication process. Intel also mentioned two “Sunny Cove” successors, the first is “Willow Cove”. It will be an incremental update, allowing for more effective IPC by improving on-die caches, transistor optimization, and the addition of new security features. The first “Willow Cove” products will arrive in 2020 and will be based on a refined 10 nm process node.

The second successor is “Golden Cove”, which is slated for 2021. Intel could be using a newer fabrication process here, either an extremely refined 10 nm or even 7 nm. This will increase IPC, but also Intel plans to improve the core’s “AI performance”, and improved host-signal processing for 5G and networking.