GPUs require a significant amount of memory bandwidth to achieve optimal performance. That’s why discrete GPUs (Graphics Processing Units) are equipped with high-bandwidth memory like GDDR or HBM, along with wide memory interfaces. In contrast, integrated graphics do not have the luxury of dedicated high-bandwidth memory. Instead, they have to share a less efficient main memory interface with the CPU cores, which may result in lower overall performance due to the limited bandwidth available.

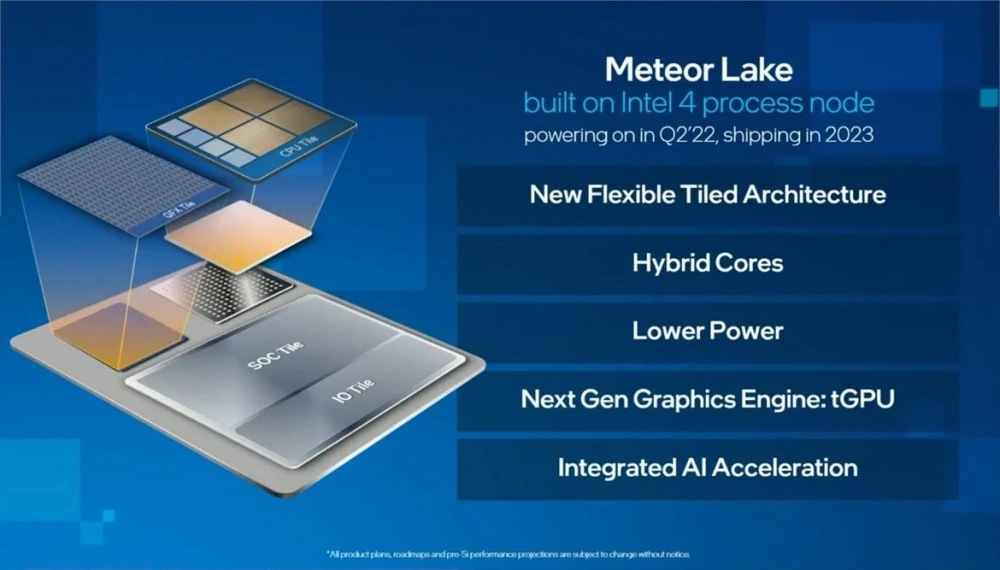

In the past, integrated graphics on Intel CPUs could utilize the CPU’s last-level cache (LLC) to assist with graphics operations that require low latency and high bandwidth. However, this approach may not be feasible with Intel’s upcoming generation of processors due to their tiled architecture. The CPU’s L3 cache will be located on the compute tile, which would require the GPU to cross the base tile to access it, making it impractical for graphics operations.

Having no cache at all would severely impact the performance of the GPU. Even discrete GPUs rely on substantial caches for efficient data manipulation. While the GPU tile for Meteor Lake, based on Arc Alchemist architecture, is expected to have some L1 cache on-die, it will likely require a larger cache for optimal performance. Thankfully, a leaked information from Intel’s Fei Yang reveals that the 14th-generation CPUs from Intel will include an L4 cache specifically for this purpose.

In response to a post on the intel-gfx mailing list, Yang commented that the integrated graphics on Intel, referred to as “GT,” will no longer be able to allocate on the LLC (last-level cache), and only the CPU will have that capability. He further mentioned that this change, along with the inclusion of support for ADM/L4 cache, will necessitate updates to the Linux graphics driver.

The exact meaning of “ADM” is not known, and there are various speculations such as “All Device Memory” or “Arc Discrete Module.” However, it is clear that “L4 cache” refers to a cache level. This information was leaked through a Japanese-language hardware blog called Coelacanth’s Dream, where the author speculates about the function and placement of the L4 cache. The author also mentions that the last time Intel processors had an L4 cache was with the Crystal Well eDRAM package on certain older CPUs.

It is worth noting that the L4 cache in Crystal Well eDRAM package served as a “memory-side” or “system-level” cache, which means it cached all types of memory accesses by any part of the System on Chip (SoC). However, the speculated L4 cache on Meteor Lake is believed to be a more traditional last-level cache specifically designed for the CPU and GPU cores. Based on similarities with Intel’s Ponte Vecchio datacenter GPUs, it is anticipated that the L4 cache will be located in the “Base Tile” of the processor, which serves as the foundation for the functional compute elements.

It will certainly be intriguing to see if these speculations about the L4 cache on Meteor Lake processors turn out to be accurate, and whether Intel will utilize the size of the L4 cache as a differentiating factor among different Meteor Lake processor models. Additionally, the impact of the L4 cache on overall processor performance, including both CPU and GPU performance, will be closely observed. Rest assured, once we get our hands on the 14th-gen silicon, we will thoroughly investigate these aspects to better understand the implications and potential benefits of the L4 cache in Intel’s upcoming processors.

Via HotHardware