At today’s “New Horizon” event AMD formally launched its Radeon Instinct MI60 GPU-based compute accelerator and disclosed some information about its next-generation “Zen 2” microarchitecture. The Instinct is the world’s first GPU built on the 7nm silicon fabrication process and one of the first commercially available products built on 7 nm. “Rome” is on track to become the first 7nm processor based on the Zen 2 architecture.

The Radeon Instinct MI60 is based on a 7nm version of the “Vega” architecture. It is not an optical shrink of “Vega 10” and could have more packed inside as well as an HBM2 memory interface that is twice as wide and can hold double the memory. It will also feature on-die logic that will enable hardware virtualization.

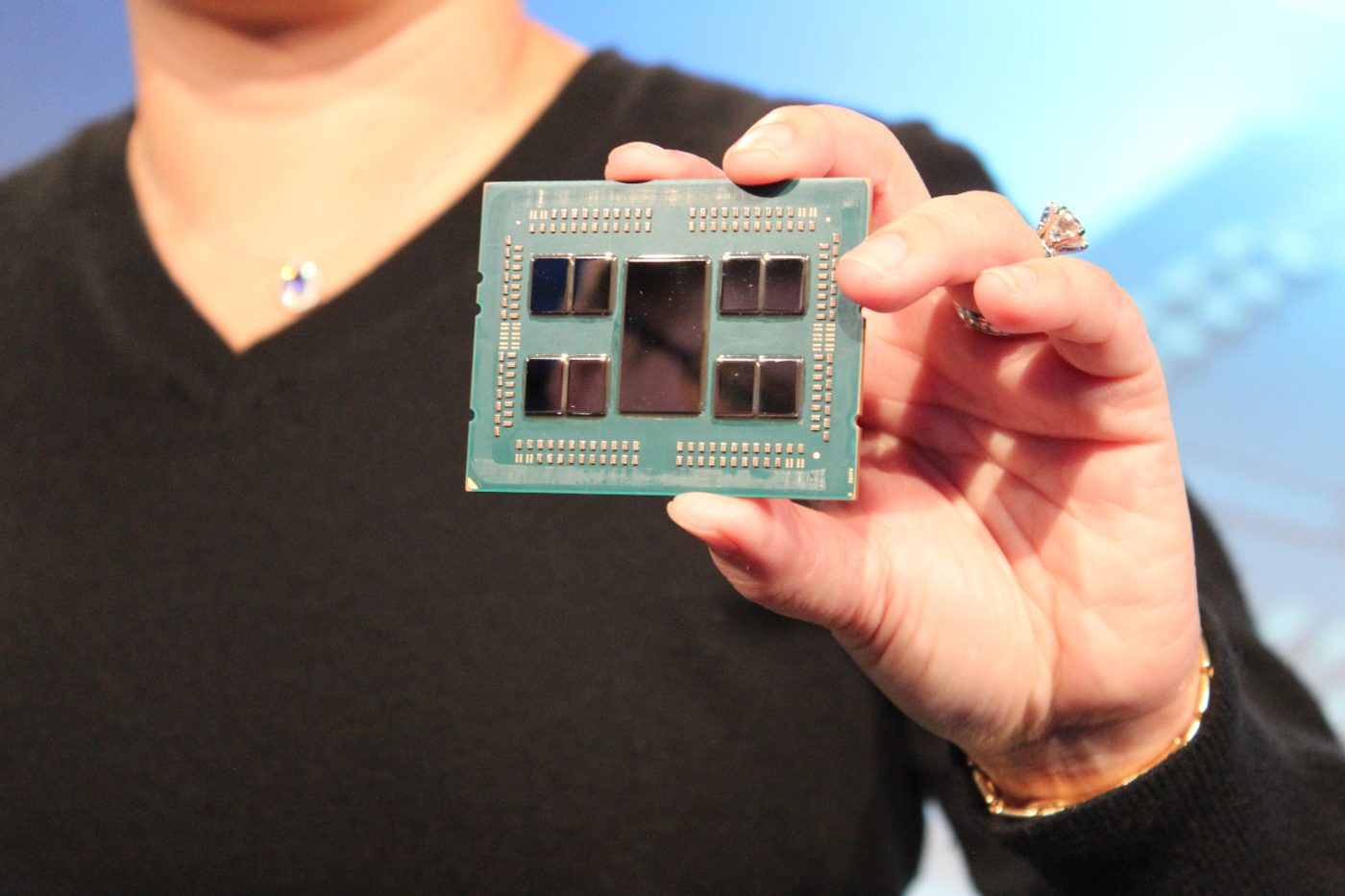

“Rome” is the codename AMD is giving for a multi-chip module of four to eight 7nm dies, wired to a centralized die over InfinityFabric. This is a 14nm die called an “I/O” die, which handles memory and PCIe, while providing an 8-channel memory interface, which overcomes the memory bandwidth bottlenecks of current-generation 4-die MCMs.

If we assume that each 7nm die has 8 CPU cores then “Rome” could have up to 64 cores, an 8-channel DDR4 memory interface, and a 96-lane PCI-Express gen 4.0 root complex, per socket. If AMD has decided to increase core-count per die, then we could see Rome’s core count go even higher.

AMD has mentioned “Increased IPC”, which is great for the client-segment. With several on-die enhancements to the core design AMD will provide an increased IPC over the previous generation. These include an improved branch-predictor, a faster instruction prefetcher, an improved/enlarged L1 instruction cache, and an improved prefetcher cache (L2).

AMD is also over-hauling the number-crunching machinery and floating point unit. With “Zen 2” you are going to get 256-bit FPUs, which are doubled in width compared to Zen. load/store/dispatch/retire bandwidths have been doubled over the current generation too. These changes are quiet impressive. Given that even without these core-level changes, by simply improving cache latencies, AMD managed to get a ~3% IPC uplift with “Zen+,” one can expect double-digit percentage IPC gains with “Zen 2.” Higher IPC, combined with possible increased core counts, higher clock speeds, and power benefits of switching to 7 nm make AMD’s “Zen 2” something to really look forward to.